미니 TSMC, N3B/N3E 관련 정보

- 좌지우건

- 조회 수 2578

- 2023.05.30. 13:07

WikiChip의 TSMC IEDM 논문 분석 내용입니다.

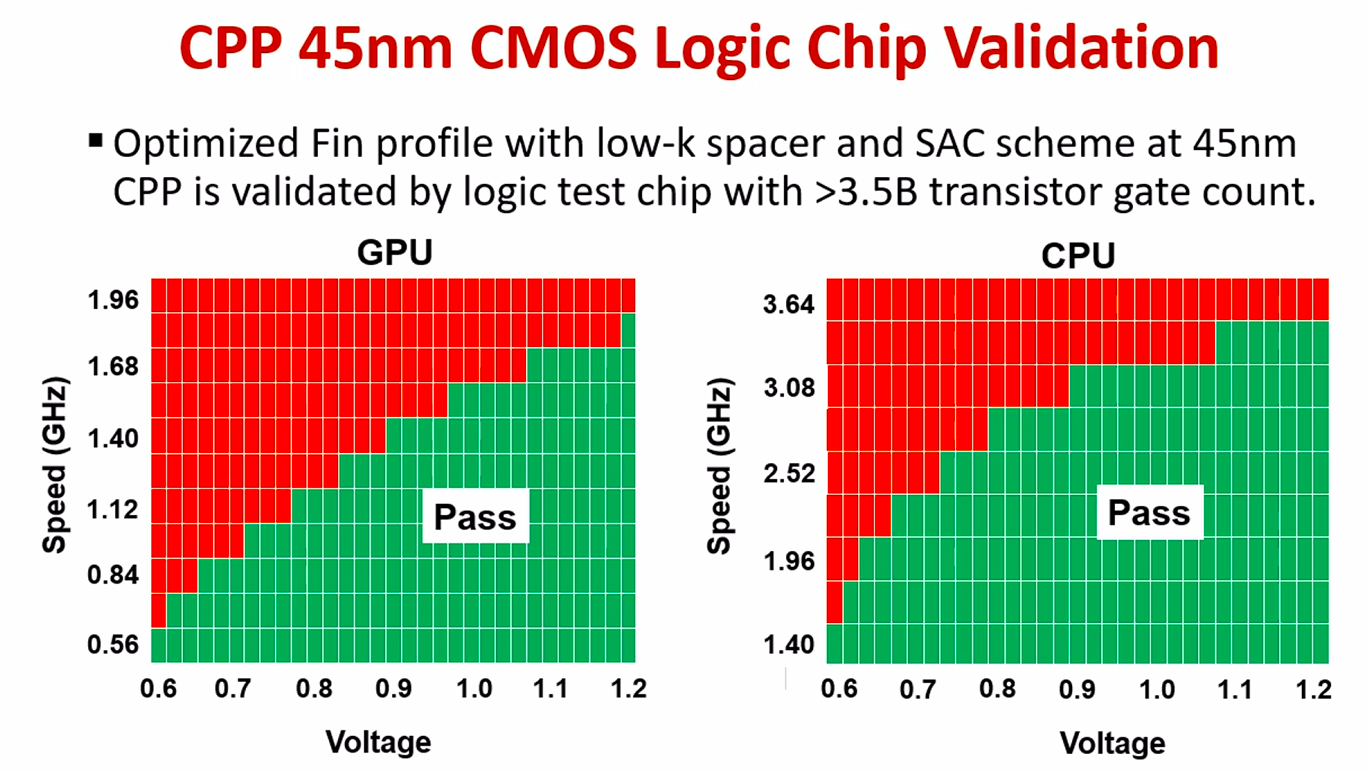

N3B

- 45 CPP (파운드리 업계에서 가장 타이트한 CPP)

실제 공정구현 수준은 45~47nm 수준으로 예상

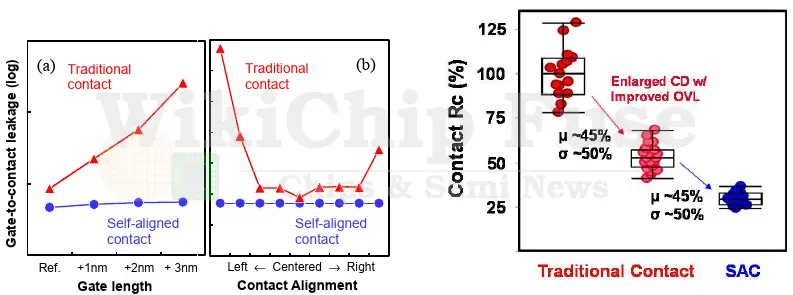

-SAC 공정 도입

타이트 한 CPP의 영향으로 Contact 공정의 이슈를 해결하기 위해 도입

실제 SAC 공정의 의한 개선

해당 기술은 인텔은 22nm, 삼성은 7nm에서 도입 이력이 있음

- Low K Spacer

Spacer 두께가 얇을 수록 성능관점에서는 좋으나(Contact 저항 개선) 수율과 신뢰성 문제 발생

그래서 TSMC는 K-Value < 4.0 조건의 Spacer를 양산도입

실제로 TDDB 사양을 통과하면서 이전 Spacer 구현에 비해 최대 230mV Vmax를 개선

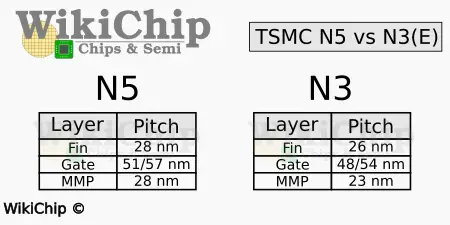

N3E

- N3B와 별개의 공정(DR이 달라짐)

- Design Length

- 공정 개선

innovative liner for Cu를 도입하여

nominal metal은 20% RC 딜레이 개선

2x metal은 30% RC 딜레이 개선

innovative barrier process를 도입하여

Via 60% RC 딜레이 개선

6세대 replacement metal gate process; N3B에서 언급한 Spacer 개선점 포함 등 여러 추가 공정개건점 적용

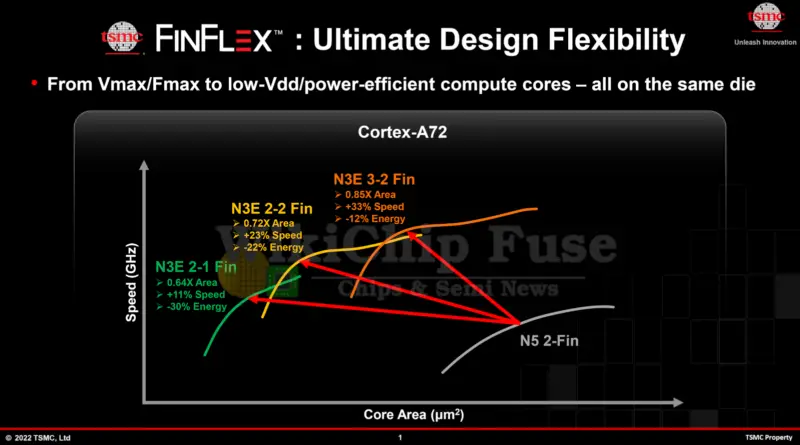

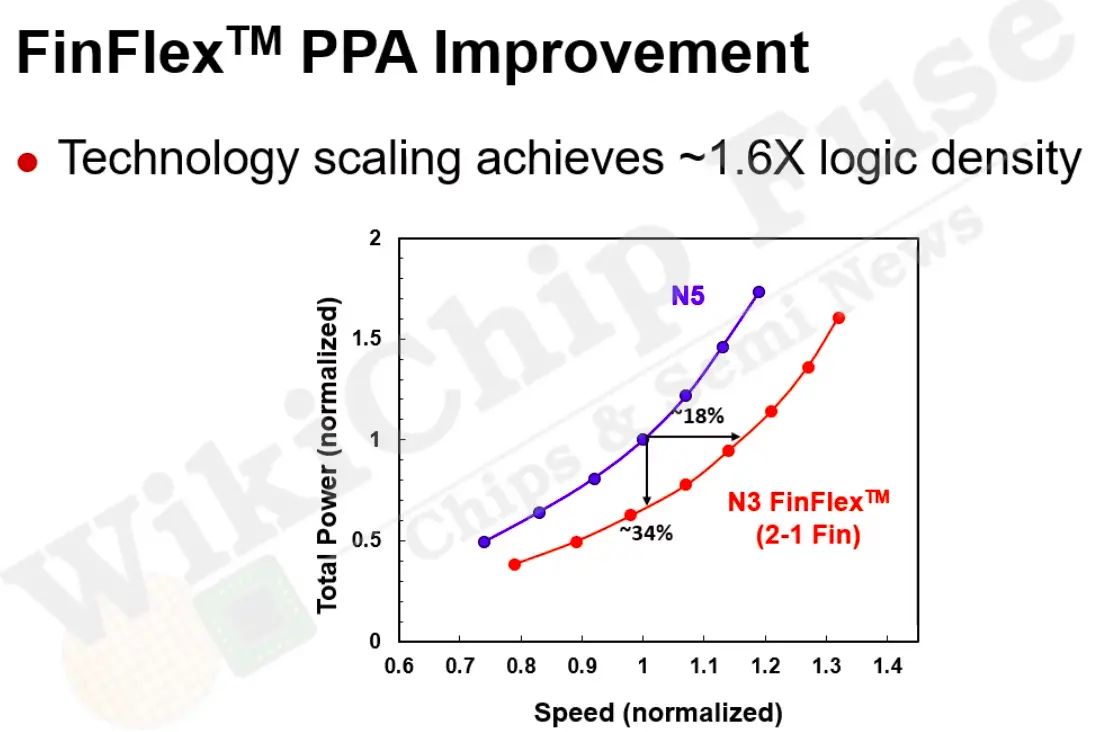

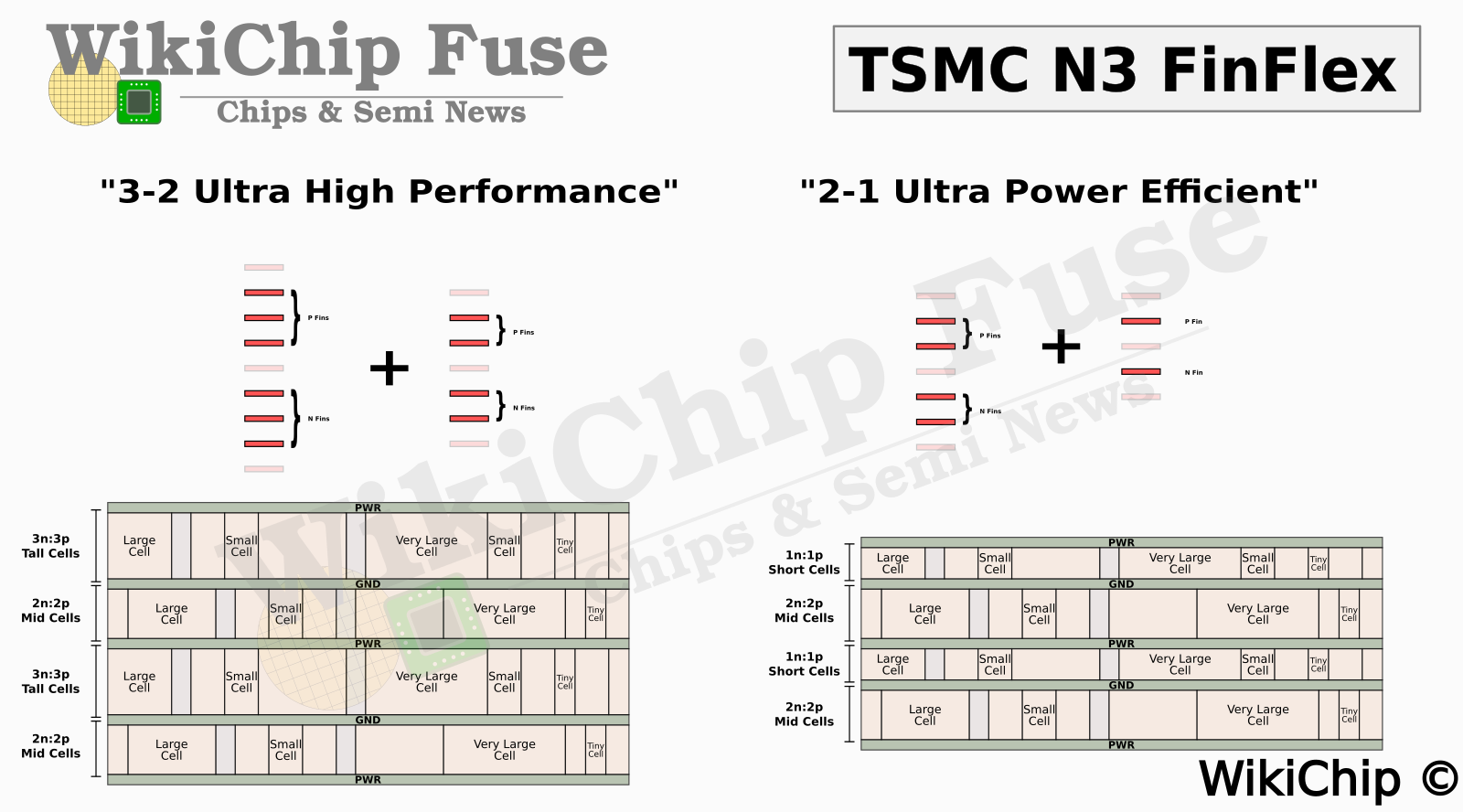

- FinFlex

다양한 조합의 Fin 구성을 통해 여러가지 Cell 옵션을 제공 이를통해 PPA 개선을 추구

Cell Option

CH143 x 48CPP

CH195 x 54CPP

CH169 x 48CPP

CH221 x 54CPP

CH286 x 48CPP

CH403 x 48CPP

CH455 x 48CPP

CH390 x 54CPP

CH559 x 54CPP

CH611 x 54CPP

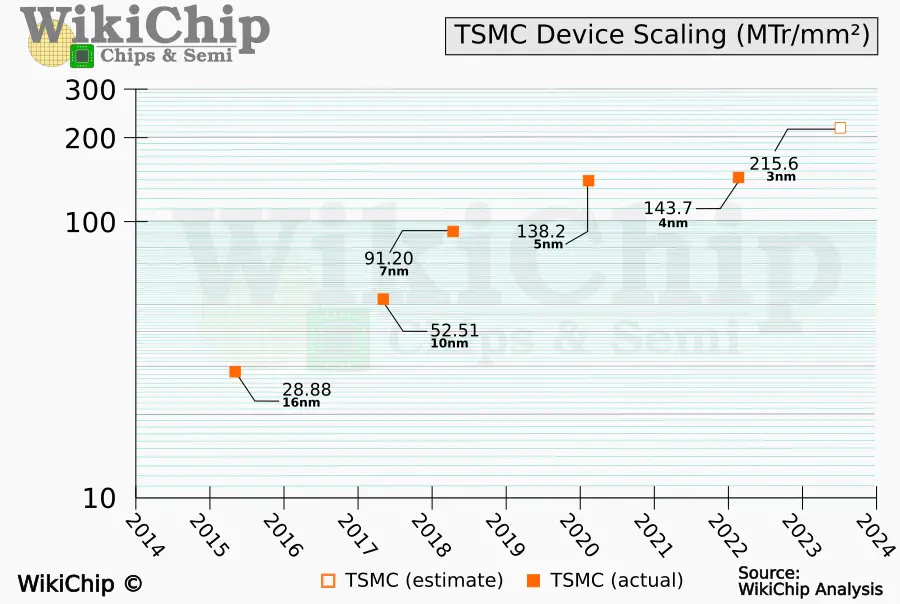

CH143 x 48CPP 기준 TR Density 215.6 MTr/mm2

CH169 x 48CPP 기준 TR Density 182.5 MTr/mm2

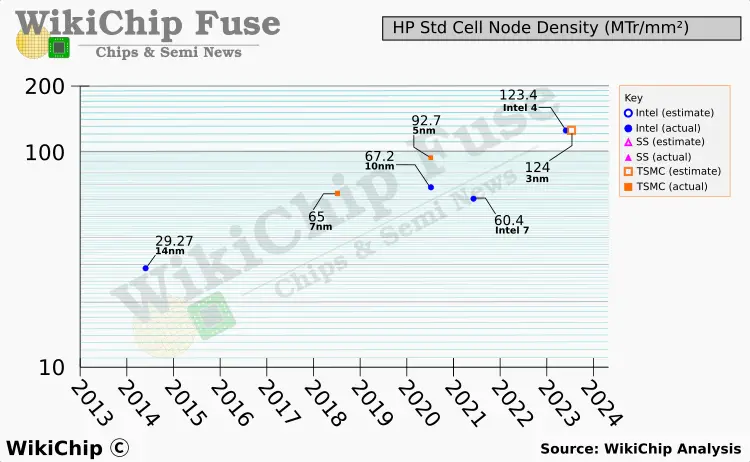

CH221 x 54CPP 기준 TR Density 124.02 MTr/mm2

(이는 Intel4 HP Cell과 유사수준)

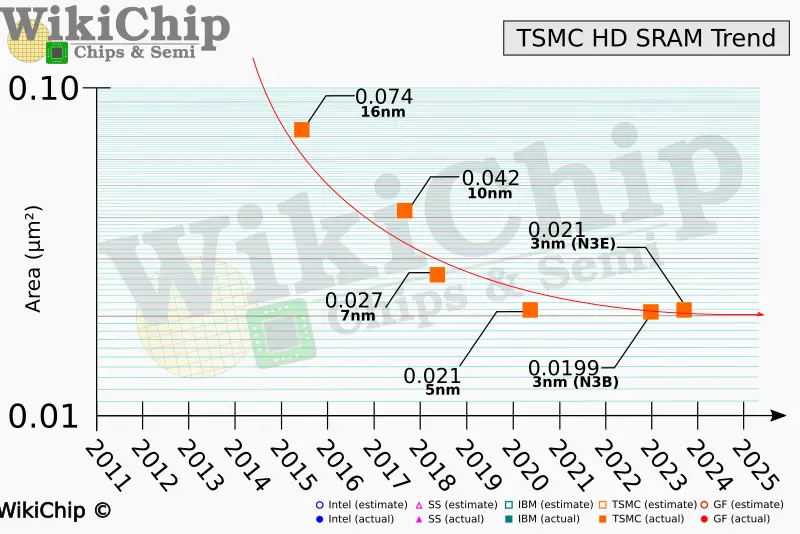

SRAM

N5 대비

- N3B 5% Scaling

- N3E No Scaling

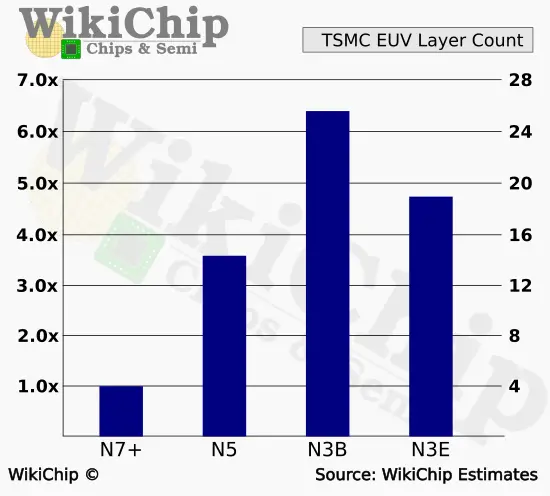

Cost

- N3B는 N5대비 상단한 발전이 있는것은 맞으나

EUV Layer 80% 수준으로 늘어 25개의 EUV Layer

(그나마 25개가 된것도 SAC도입 덕분 SAC이 없었다면 26개를 돌파 했을 수도)

- N3E는 더 느슨한 피치를 적용하여 EUV 더블 패터닝이 필요했던 3개의 Layer를 싱글 패터닝으로 전환

이를 통해 Line과 Via를 포함 6장의 Layer를 줄여 36% 절감 달성

비전공자라 무슨 말인지는 모르겠으나 대단하다는건 알겠습니다 ㄷㄷ