예전부터 관련 내용을 상세히 포스팅을 해보고싶었는데, 기회가 된거같아서 정리해보았습니다.

이미 보신 분들은 아시겠지만 저번달 9월 16일 17nm로 CIS 제조 시 어떤 장점이 있는지에 대해 간단히 글을 올린적이 있습니다.

https://meeco.kr/mini/36034676

필요한 내용은 다있지만 글만 봐서는 크게 와닿지 않을겁니다.

설득력도 많이 떨어지구요.

보는이로 하여금 초고화소 CIS에 대한 단점을 쉴드치는거처럼 보일수도 있습니다.

이부분은 저도 인지하고 있는 부분이라 좀 더 심도있게 다뤄보려고 합니다.

제목처럼 17nm FinFET 공정 적용에 앞서서

CIS 내부 구조 관련해서 이야기를 먼저 해볼까 합니다.

이걸 먼저 다뤄야 FinFET 공정이 적용되었을때

이점을 더욱 명확하게 이해할 수 있을테니깐요.

[CIS는 무엇인가?]

CIS는 CMOS Image Sensor의 약자로

카메라 부품 중 흔히 말하는 "이미지 센서"에 해당됩니다.

카메라 렌즈를 통해 들어온 영상 정보를 감지하고 이를 디지털 신호로 변환하는 장치이고

사람으로 치면 눈의 "망막"에 해당됩니다.

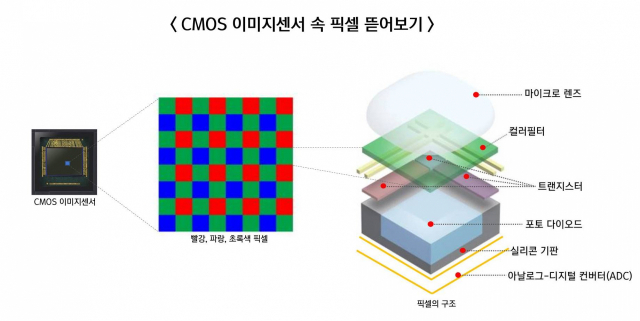

이 CIS 내부 구조에 대해 자세히 살펴보면..

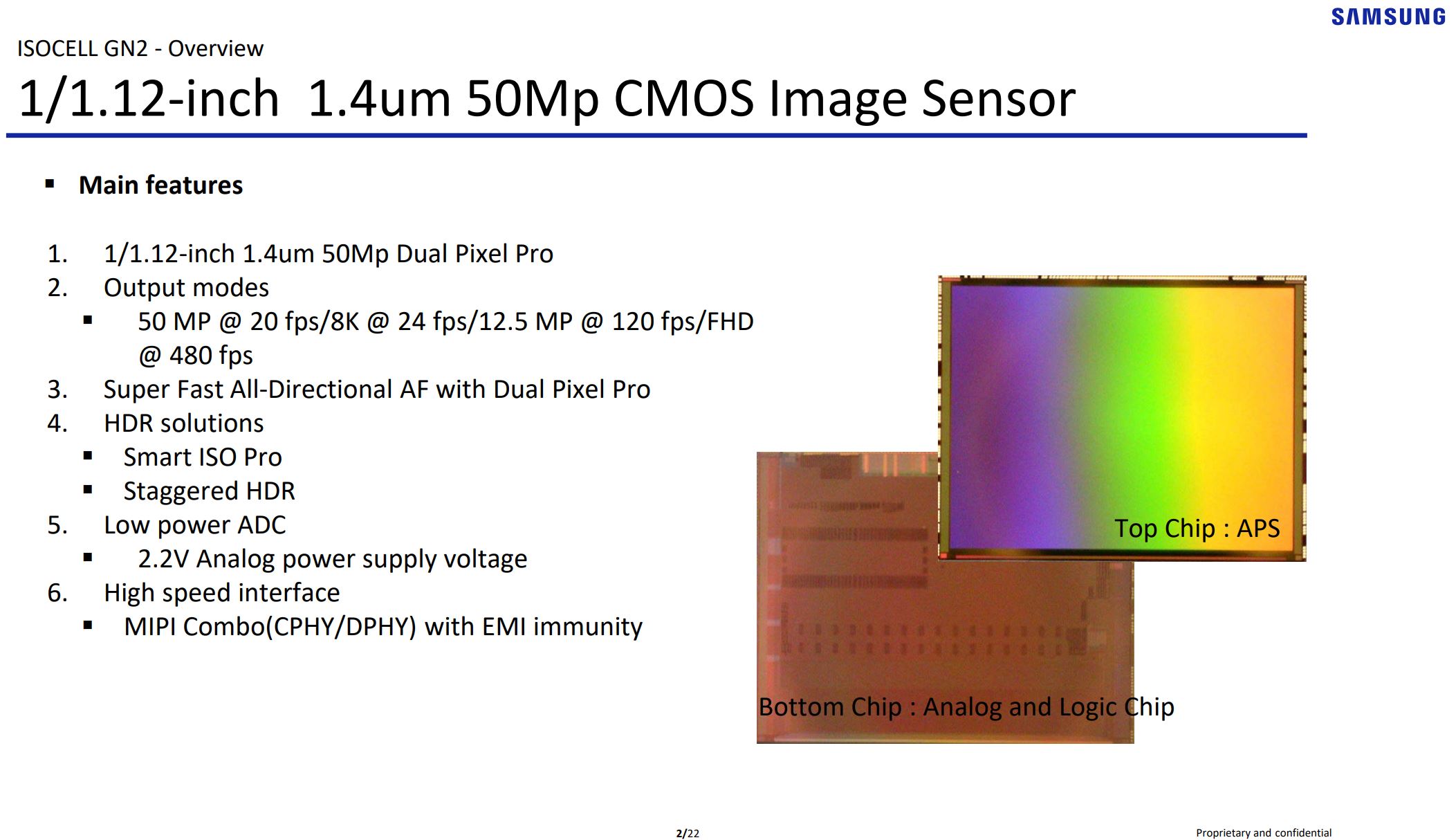

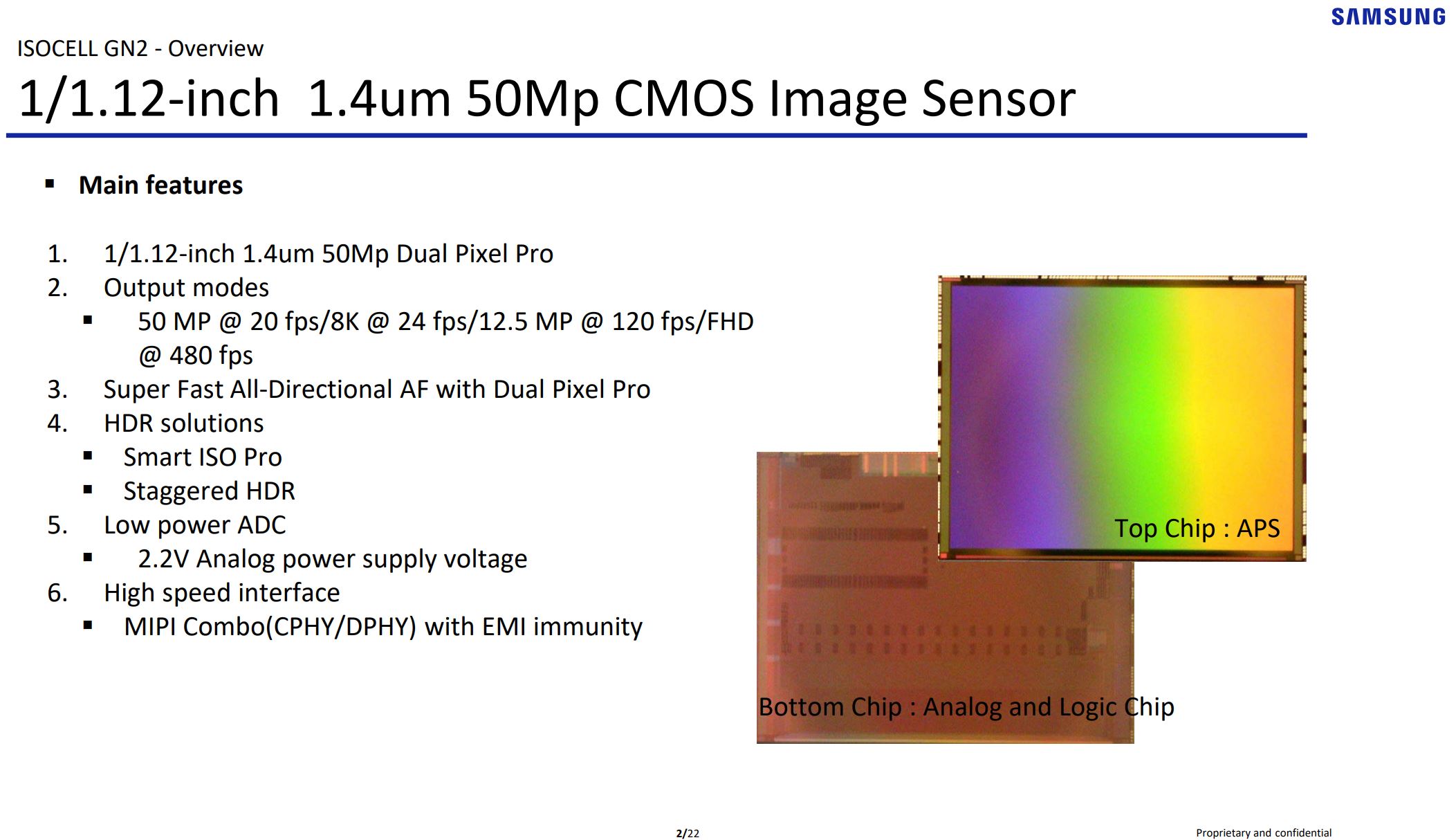

※ ISOCELL GN2 기술발표 자료 첨부

CIS는 보시는거처럼

상판(TOP Chip)으로 불리우는 수광부 기판(일명 APS)과

하판(Bottom Chip)으로 불리우는 로직 기판이 있습니다.

이 둘을 합쳐서 CIS가 완성되는 것이지요..

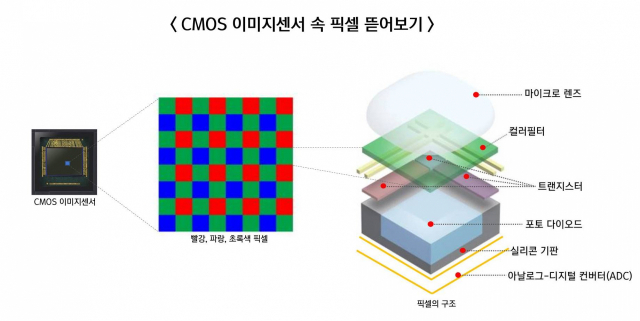

상판의 수광부 구조를 먼저 살펴보자면

이미지처럼 마이크로 렌즈, 컬러필터, 트랜지스터, 포토다이오드, 아날로그-디지털 컨버터 등으로

구성되어있고 화소 관련된 모든게 상판 수광부 기판에 들어가있다라고 보면됩니다.

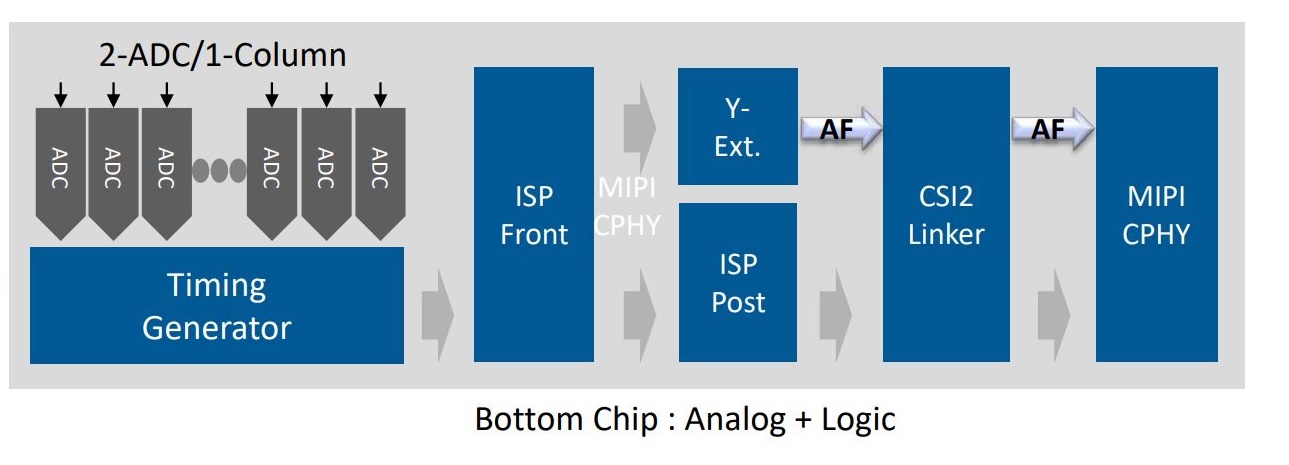

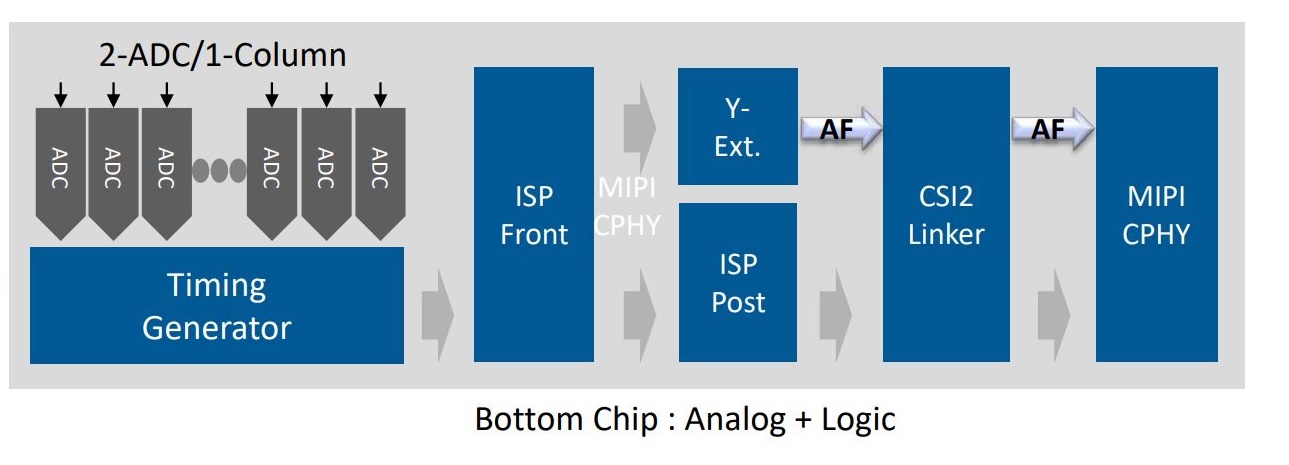

다음은 하판의 로직 입니다.

많이들 놓치고 가는 부분인데 CIS에는 이미 하판에 ISP(image signal processor)가 들어가있습니다.

상판의 수광부에서 받은 결과물을 디지털 이미지로 처리해주는게 바로 로직 기판의 역할입니다.

상판이 화소와 관련되서 사실상 메인이지만

작디 작은 모바일 CIS에서 이 로직 성능이 정말 정말 중요합니다.

특히 모바일 CIS는 수광부 픽셀 사이즈가 워낙 작다보니 받은 결과 값을 보정해주는

로직 의존도가 중요해질수 밖에 없습니다.

반대로 판형이 거대한 디지털 카메라용 이미지 센서는 로직 의존도가 낮습니다.

이미 수광판의 픽셀 사이즈가 워낙 거대해서 빛을 워낙 잘받아서 하판 로직은

적당한 성능이면 충분하고 카메라 바디에 ISP칩이 또 별도로 달려있어서 크게 요구되진 않습니다.

다시 모바일 CIS 이야기로 돌아와서

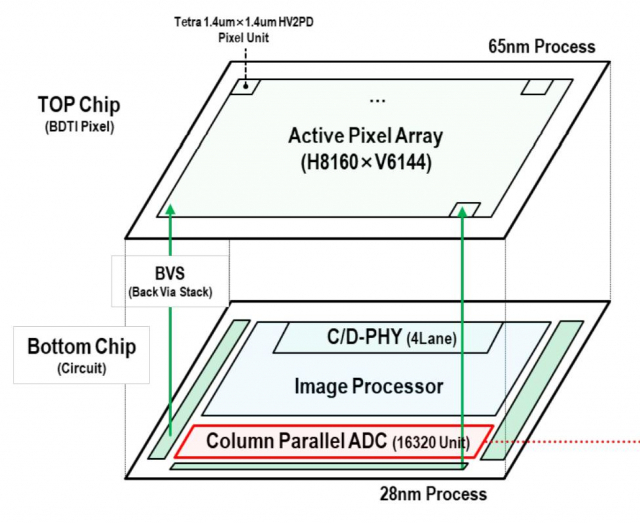

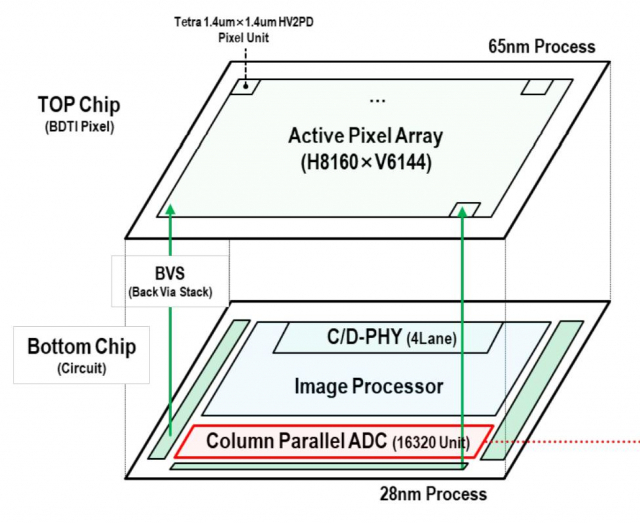

모바일 CIS는 대부분 상판은 65nm 공정으로 제조되고 하판은 28nm 공정으로 제조합니다.

※ ISOCELL GN2의 CIS 다이어그램

위에 언급한 GN2도 그렇구요.

여기서 의문이 들겁니다. "하판은 28nm인데 왜 상판은 65nm지?"

그 이유는 상판은 미세 공정으로 제조할수록 픽셀이 작아지기 때문입니다.

초고화소에 작은픽셀로 CIS를 만들게 아닌이상 상판에 최신 미세 공정을 도입할 이유는 없습니다.

로직 부분은 수광판에서 받은 결과물을 처리하기 위해 현재 기준에선 레거시지만

그나마 더 미세화된 28nm 공정을 쓰는것이구요.

[모바일 CIS에서 성능을 올리는 방법]

그동안 모바일 CIS 추세보면 로직보단 상판 수광부를 개선하는 방식으로

품질을 올려왔습니다.

대표적으로 세 가지 방법이 있는데...

1. 상판의 포토다이오드 설계 최적화 및 신소재 도입

빛을 받는 포토다이오드 설계를 최적화 하거나 신소재를 도입하는겁니다.

대표적으로 삼성 시스템 반도체가 지속적으로 하는 방법입니다.

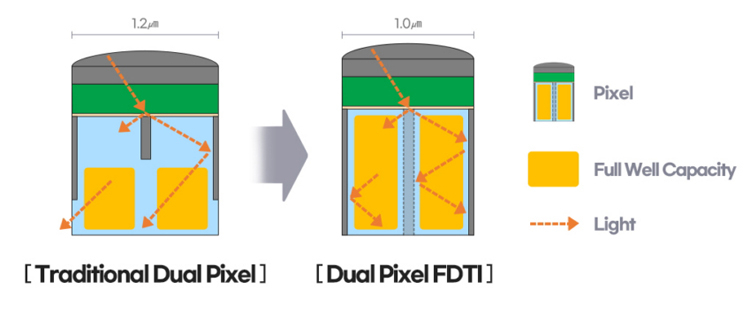

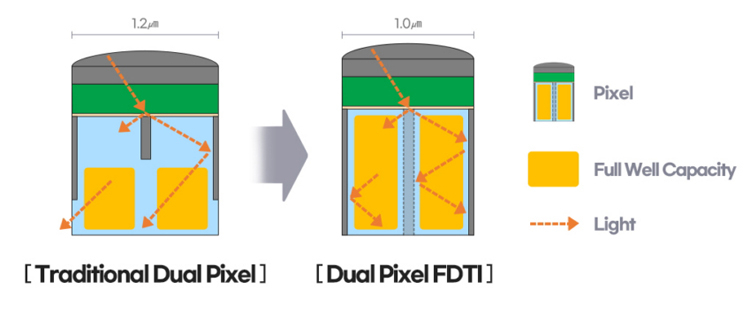

기존 대비 미세화된 픽셀 포토다이오드에 BDTI가 아닌 FDTI를 도입해서

픽셀 사이즈는 작지만 더 빛을 많이 받게하고 품질을 향상시키는 방식인것이죠

ISOCELL 시리즈가 버전을 업을 할때마다 이론상 이전 버전 대비 빛을 더 많이 받도록

꾸준히 발전 시키고 있습니다.

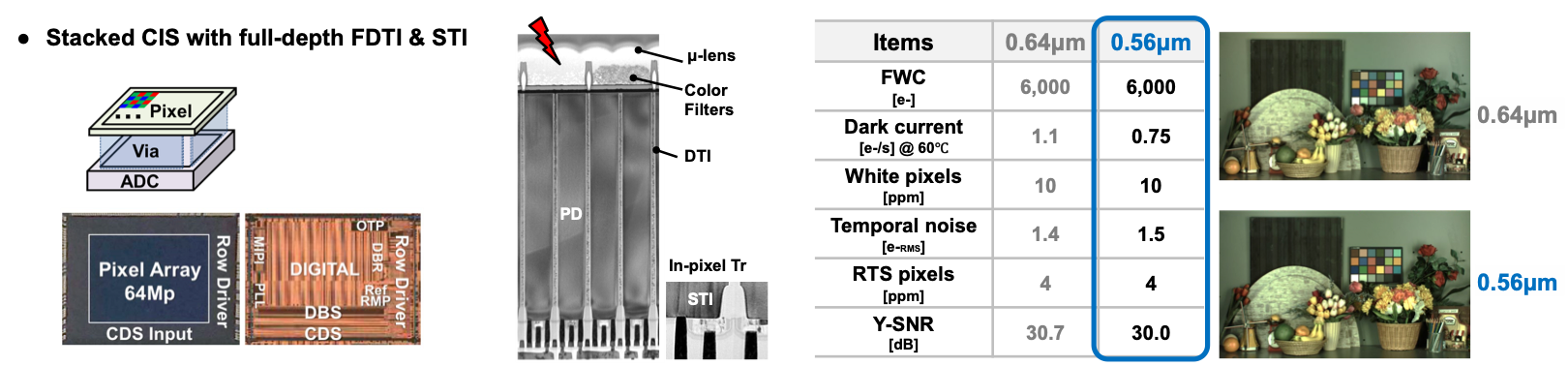

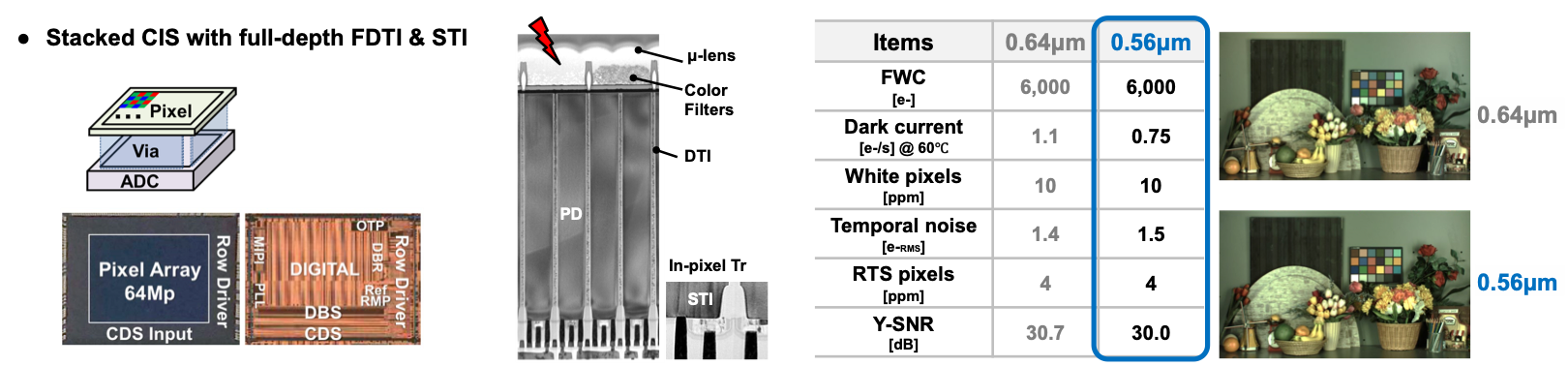

그리고 최근 가시적인 성과로 나온게

삼성 시스템 반도체가 2022년 ISSCC에서 발표한 신규 64MP 0.56um 입니다.

50MP 0.64um과 비교 시, 비슷하거나 더 나은 품질을 보여준다는 발표였죠.

(해당 부분은 64MP로 좀 더 고화소라서 그런것도 있을것으로 추정)

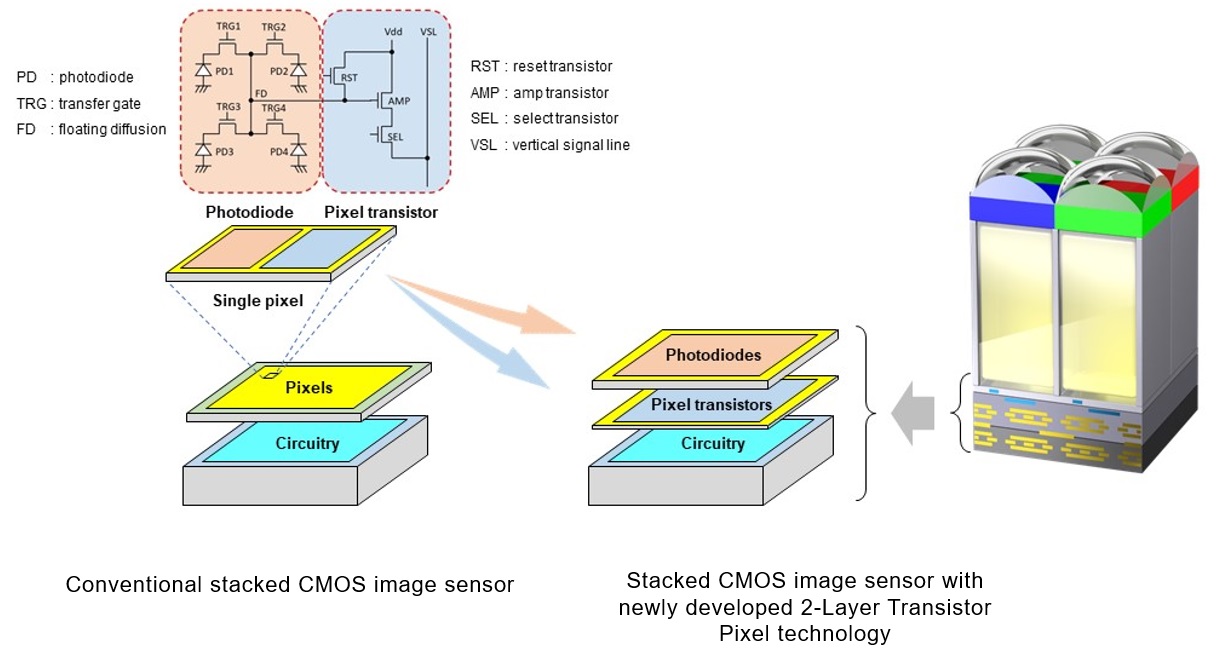

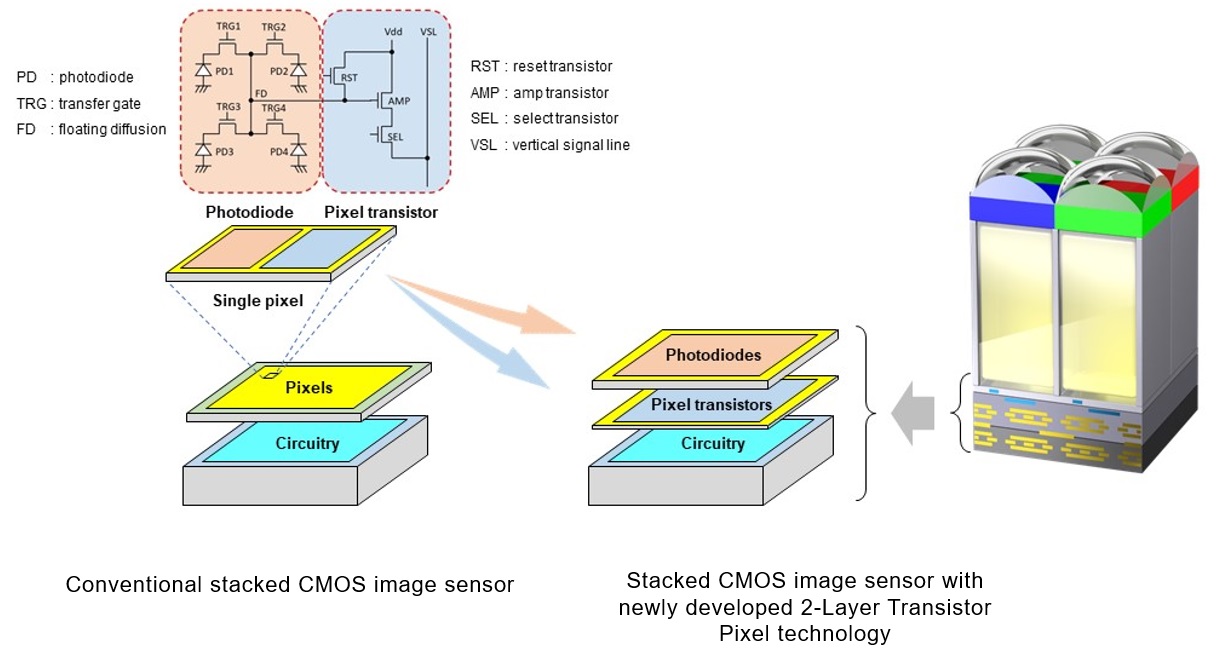

2. 상판을 2층으로 적층하기

두번째는 최근 소니가 밀고 있는 방법입니다.

기존 CIS 상판 수광부의 경우 포토 다이오드와 화소 트랜지스터를 하나의 기판으로

썼다면 2층 트랜지스터 적층은 서로 다른 기판에 형성해 적층시킴으로서 빛을

2배 잘 포착하고 다이나믹 레인지와 노이즈도 크게 개선하는것을 목표로 합니다.

현재 아이폰14 프로/프로맥스에 탑재된 48MP 1.22um 2PD CIS에 적용된 기술이기도하죠.

애플의 뛰어난 튜닝 노하우와 2층 트랜지스터 적층이 적용된 CIS덕에

48MP ProRAW나 35~48mm 화각 크롭 줌 등등 큰 성과가 있었습니다.

3. eDRAM 적용

요즘은 단가 문제로 모바일에서 잘하지 않는 방법이긴하지만 부족한 로직 성능을 충당하기 위해

12MP 2PD CIS때 많이 쓰던 방법입니다.

[초고화소 CIS에서 수광부 개선의 한계]

위에 언급처럼 그동안 CIS 제조사들은 작은 픽셀에서도 다양한 방법을 이용해서

품질을 개선해오고 세대를 거듭할수록 가시적인 성과가 나왔습니다.

그러나 48MP 이상 초고화소로 가게되면 물리적인 한계가 발생합니다.

수광부 픽셀에서 더 빛을 많이 받게해서 품질을 올린다치더라도

하판 로직에서 고화소 처리를 제대로 못하면 기껏 개선한 수광부 품질이

의미가 없어집니다.

그러면 AP의 ISP+NPU의 의존도가 높아지고 의존도가 높아지진단 소슨

원하는 품질을 얻을려면 촬영 속도 성능이 떨어진다는 뜻이됩니다.

그래서 삼성파운드리에서 제시한것이 있습니다.

[CIS 로직 기판에 FinFET 공정 도입]

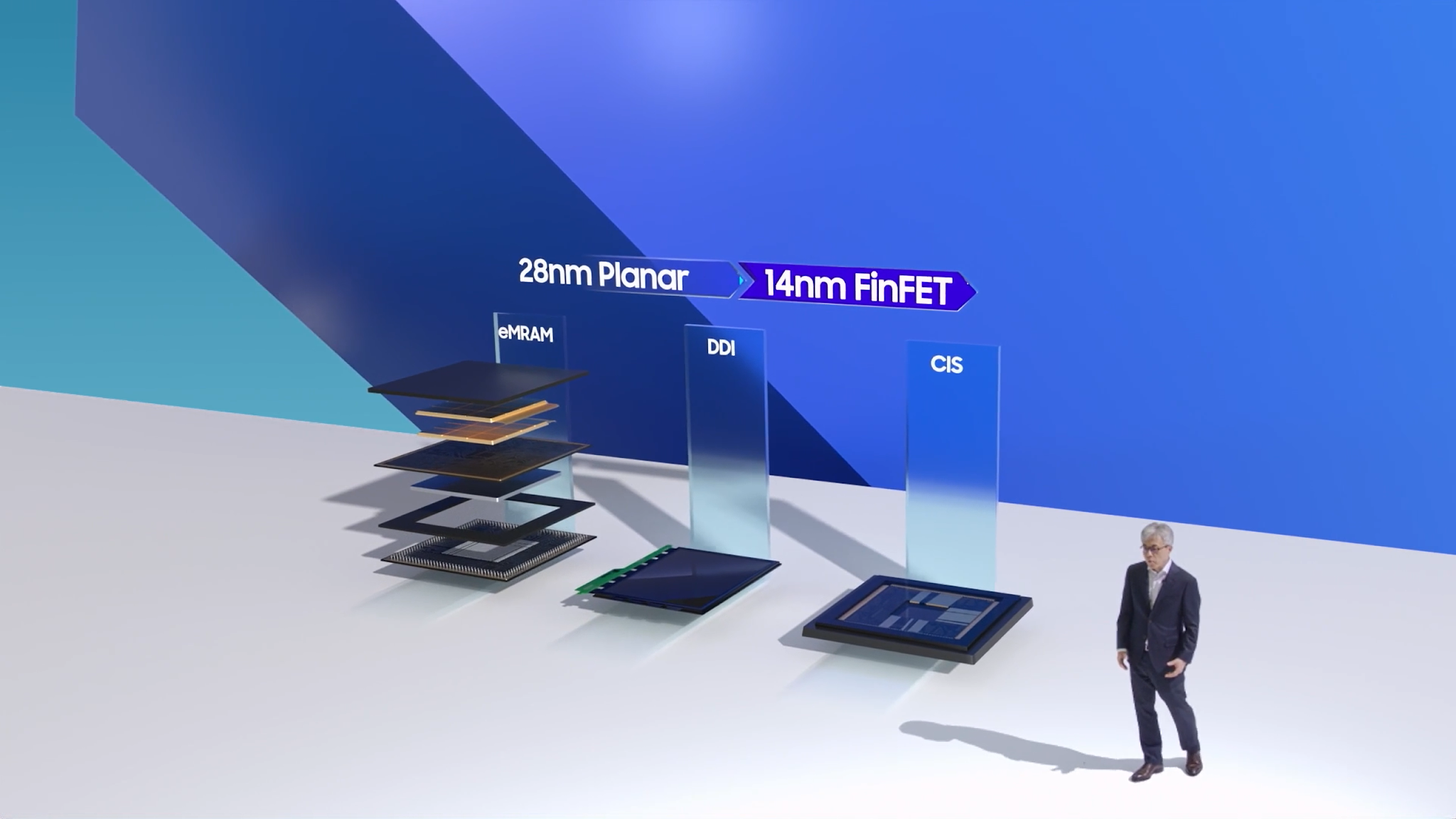

삼성은 2020년 ISCAS에서 65nm 상판과 14nm FinFET 하판으로 이루어진 CIS에 대한 기술 발표를 했습니다.

당시 레퍼런스로 제시되었던건 12MP 1.4um CIS인데

상판 수광부는 기존과 동일하게 65nm로 제조하고

하판 로직은 새로운 14nm FinFET 공정으로 제조해서

성능을 개선한다는 내용입니다.

크게 언급되는 부분은 다음과 같습니다.

- 기존 28nm 로직 대비 소비전력 29% 감소

- 12MP에서 초당 120fps 달성

- 램덤 노이즈 20% 감소

그리고 마지막 슬라이드에는 다음과 같이

FinFET Process는 이미지 센서를 위한 좋은 후보입니다!

- 65/14nm 적층 센서 구현에는 몇 가지 장점이 있습니다.

1. 전력 절감

2. 빠른 속도 외

3. 노이즈 감소

전력 예산은 8K 비디오와 200MP 이상의 센서에 매우 중요합니다!

- 아날로그 회로와 디지털 회로 모두에 대해 낮은 전원 공급 전압이 필요합니다.

미래 센서는 머신러닝과 에지 컴퓨팅을 가능니다!

- 센서 상에 주요 영상 신호 처리 기능을 구현할 수 있습니다.

=====================================================

라고 언급되고 있습니다.

슬라이드 내용만보면 나쁘지않은 수치지만

사실 저 때당시는 CIS 로직을 FinFET으로 뽑는건 수지타산에 맞지 않았을 겁니다.

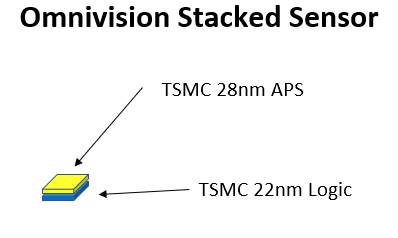

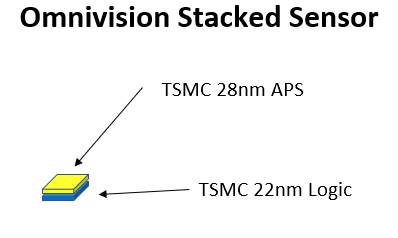

이미 TSMC 같은 경우도 28nm가 아닌 좀 더 진보된 공정인 22nm 공정인 22ULP 같은것으로도

CIS 로직을 뽑을 수 있도록 권장하지만 이조차도 단가가 비싸서 쓰이지 않았습니다.

하물며 14nm FinFET은 아무리 성능 개선하려고 하는거지만 배보다 배꼽이 더 커지는 상황이 되는거죠

그런 와중에 옴니비전이 200MP 0.56um CIS를 개발하면서

상판을 TSMC 28nm로 제조하고 하판 로직을 TSMC 22nm로 제조해서

성능을 크게 올릴거라는 발표를 했습니다.

초고화소 CIS에서 28nm 로직으로는 재성능을 못내기 때문에 선택한듯합니다.

상판의 경우도 200MP 0.56um으로 작아져서 28nm를 쓴것으로 보이네요.

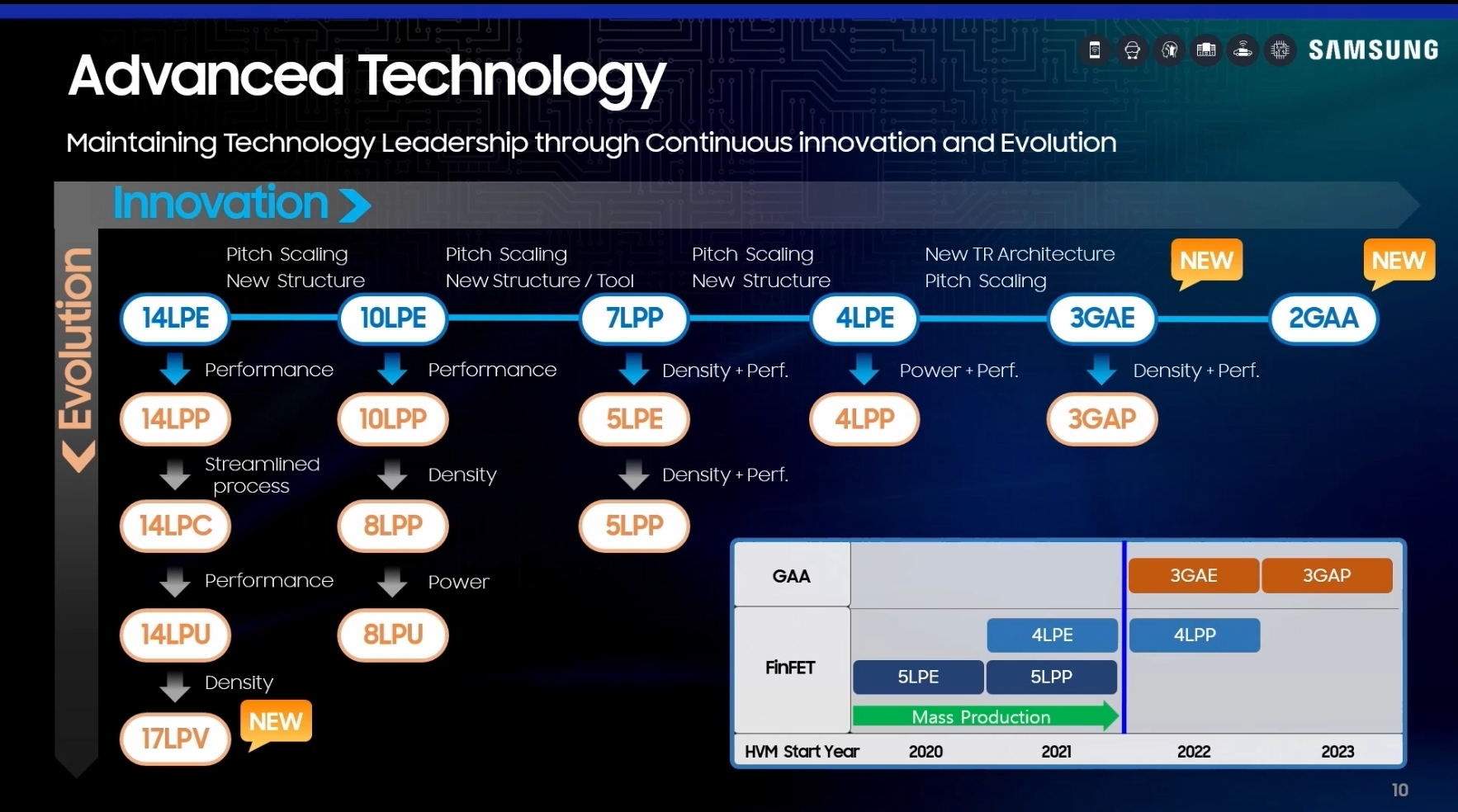

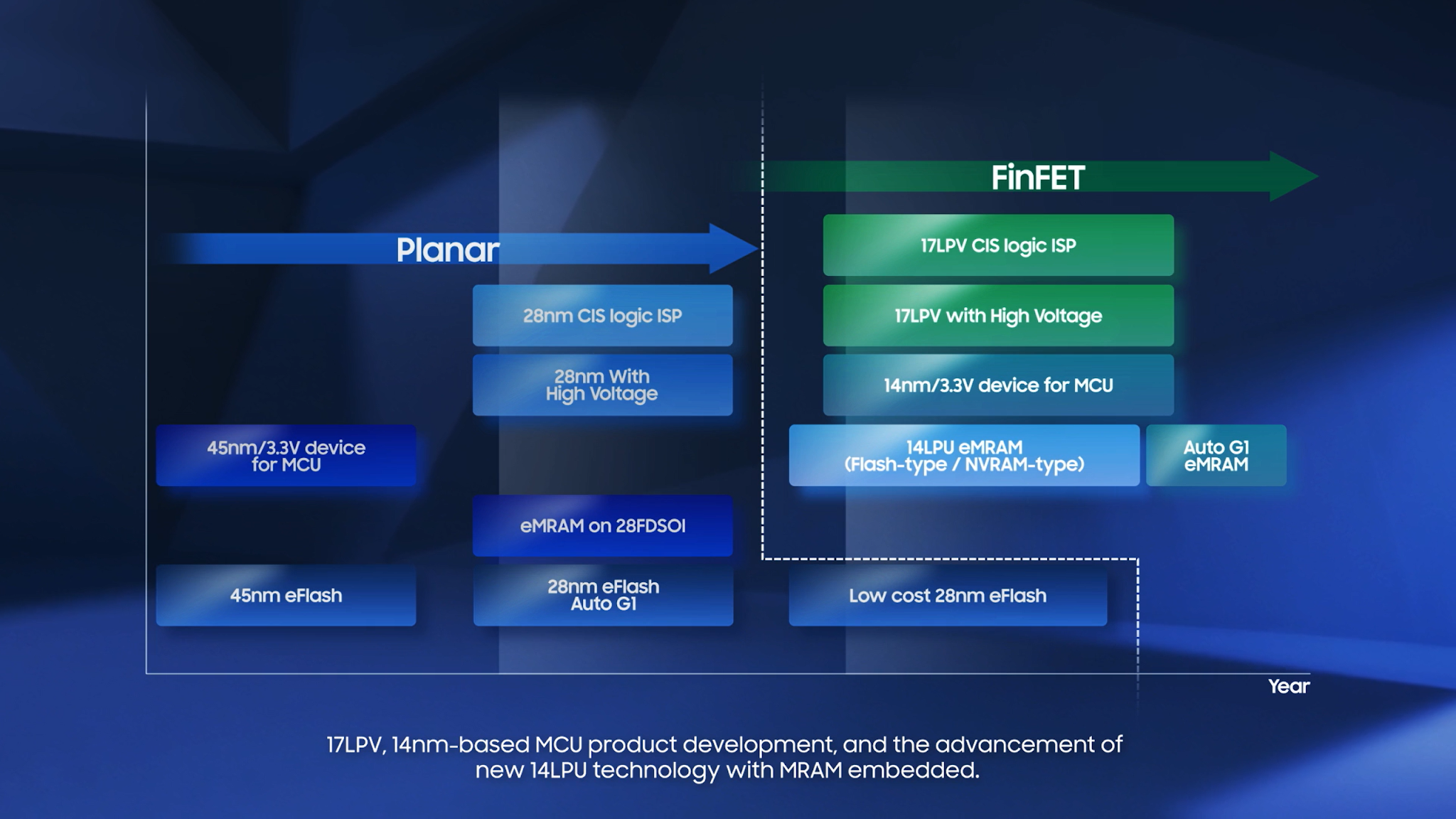

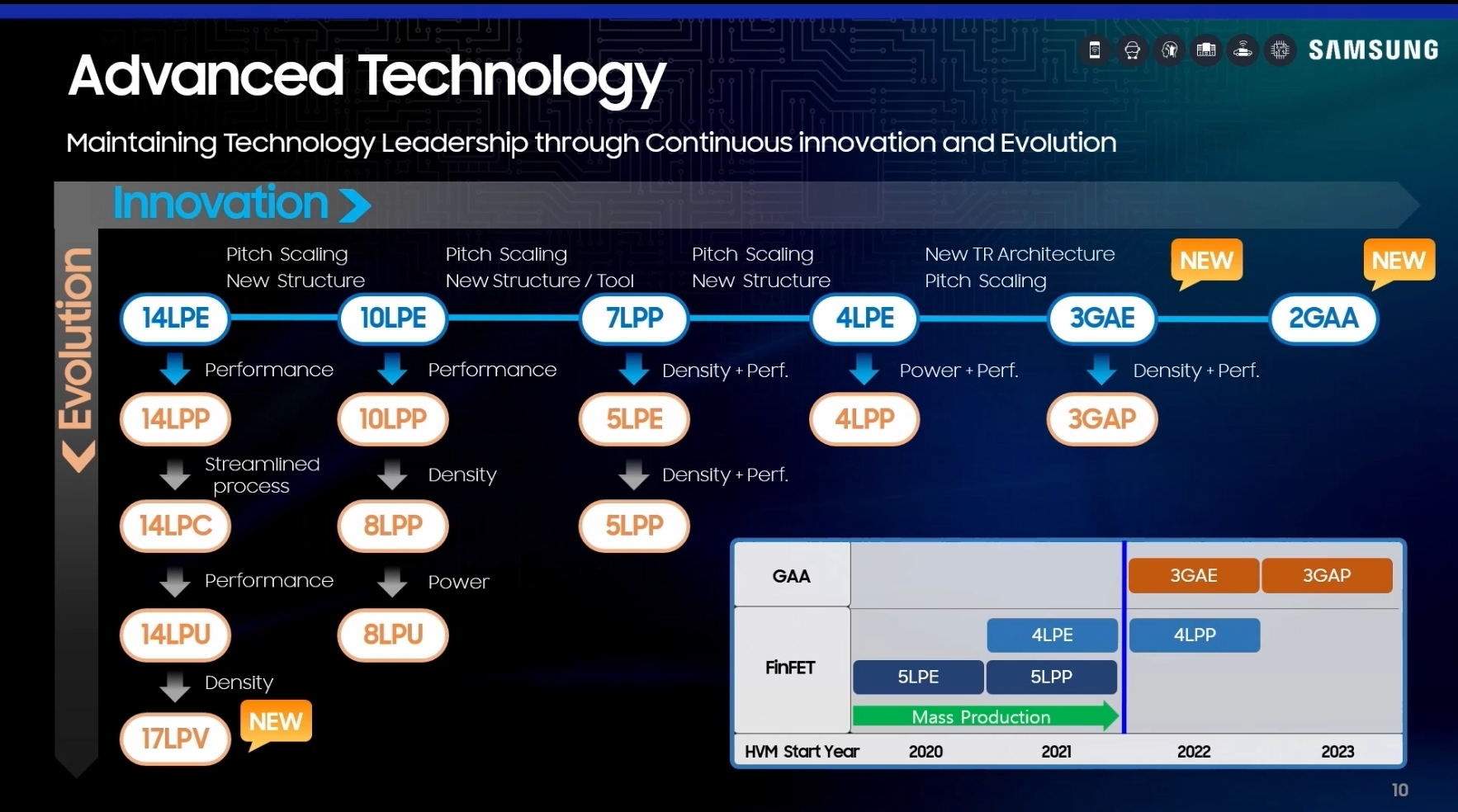

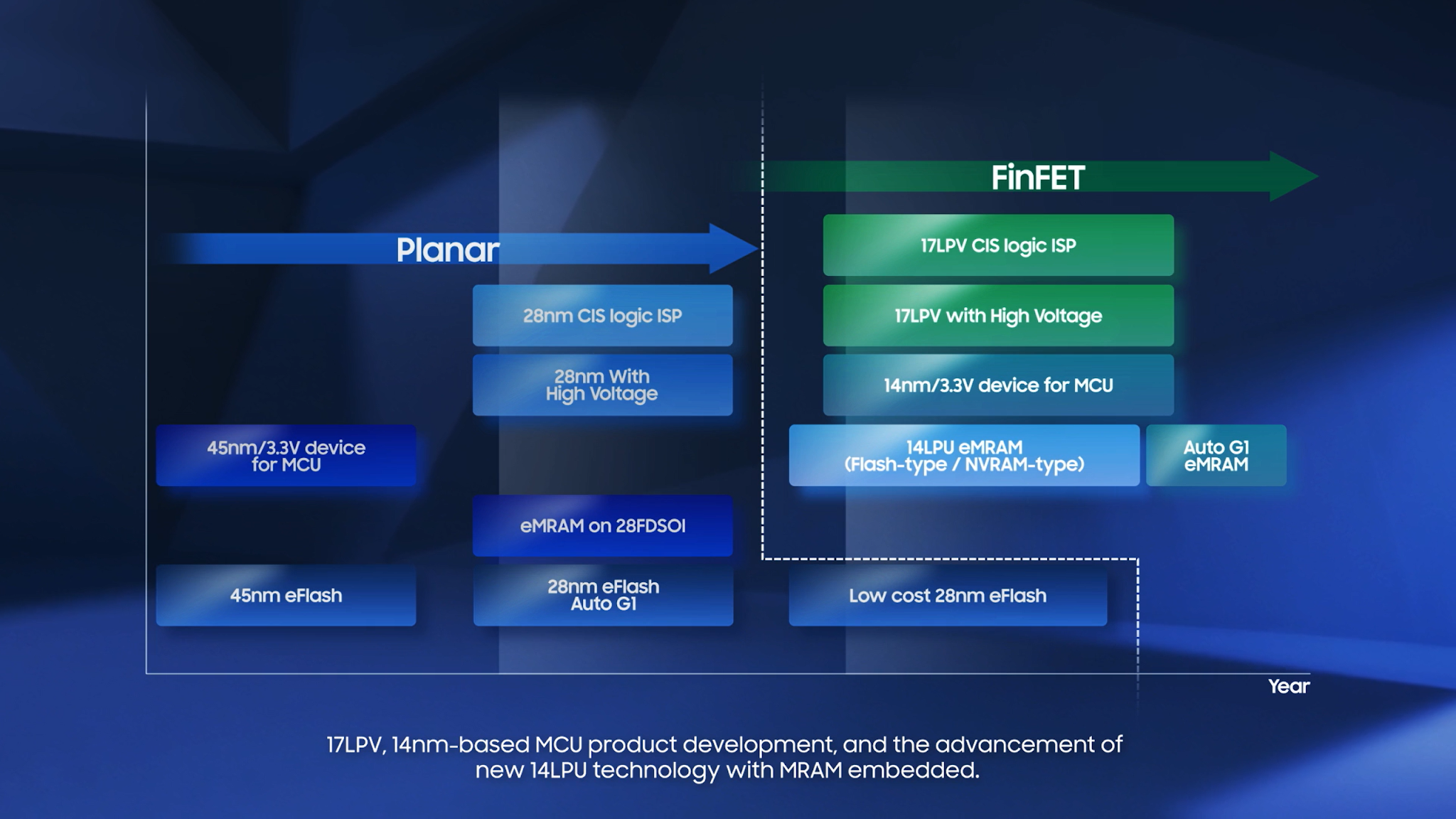

[삼성의 17nm FinFET LPV 공정 발표 차세대 CIS 로직에 도입]

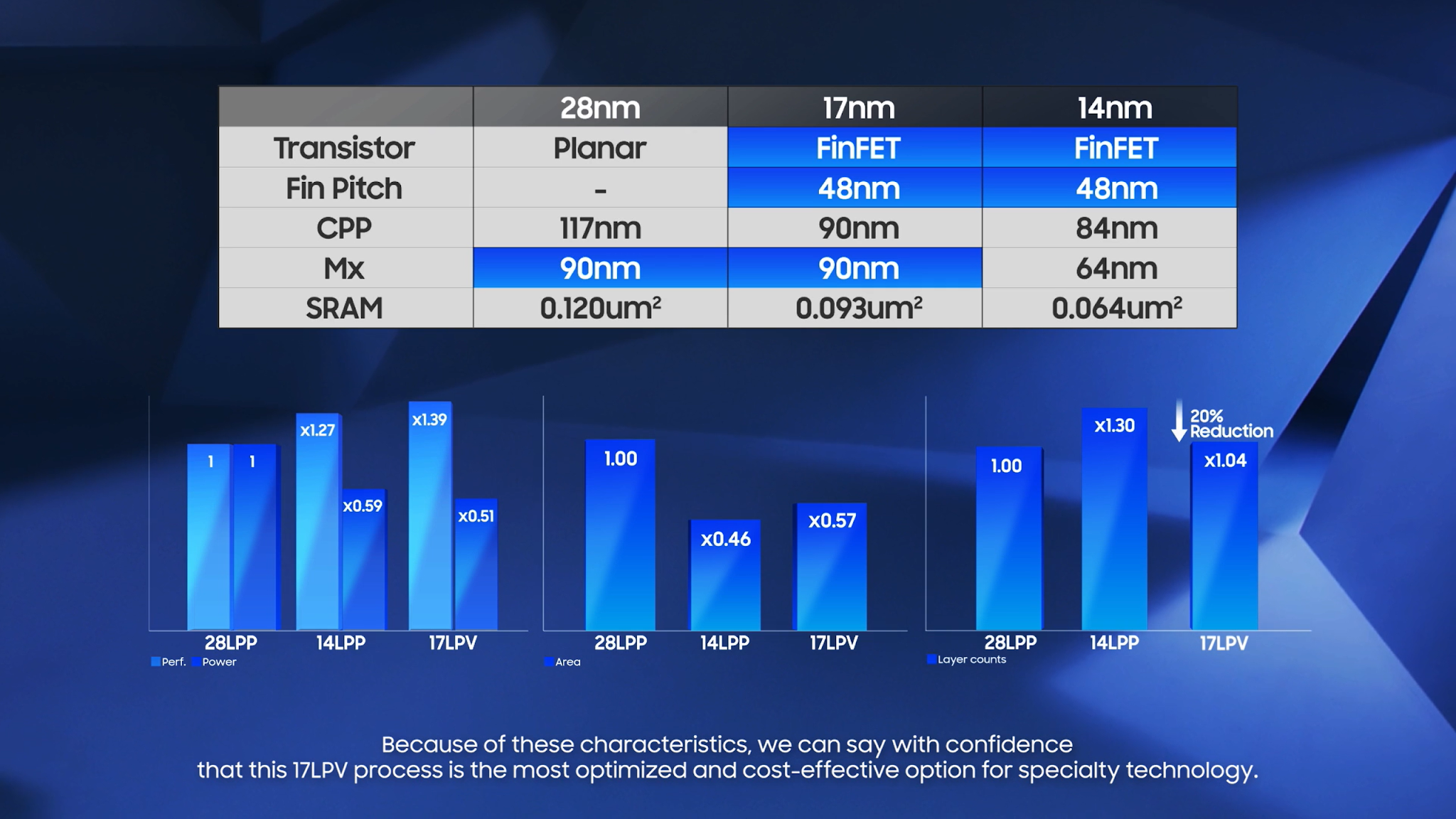

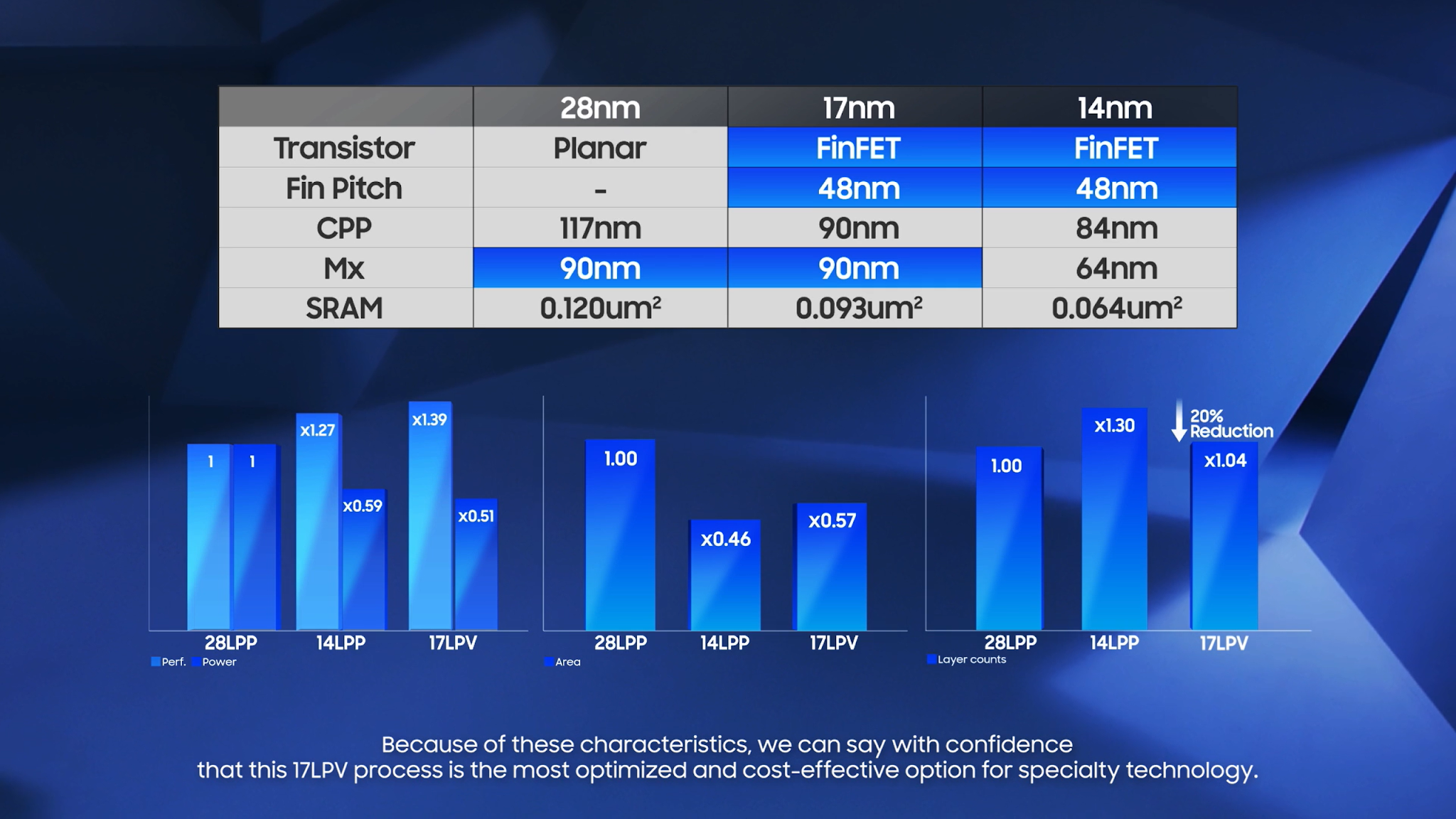

FinFET으로 CIS 로직을 뽑아낼거란 계획안을 제시한 뒤 시간이 흘러서 삼성은 14nm 베이스의 신규 공정인

17LPV 공정을 발표 합니다.

성능 외적으로 단가부분이 꽤 신경쓰였던것인지 백엔드는 기존 28nm 공정을 그대로 사용하고

프론트엔드는 14nm를 사용하는 공정이 되었습니다.

이덕분에 성능은 성능대로 크게 올리고

단가는 낮출수있었습니다.

노드 표기는 17nm라고 하고있지만, 성능은 발군입니다.

기존 28LPP 공정 대비

소비전력 51% 감소

성능 39% 향상

이란 어마어마한 수치를 기록했습니다.

단순 이 수치만 놓고보면 14LPP 공정보다 더 높은 성능을 보여주고 있습니다.

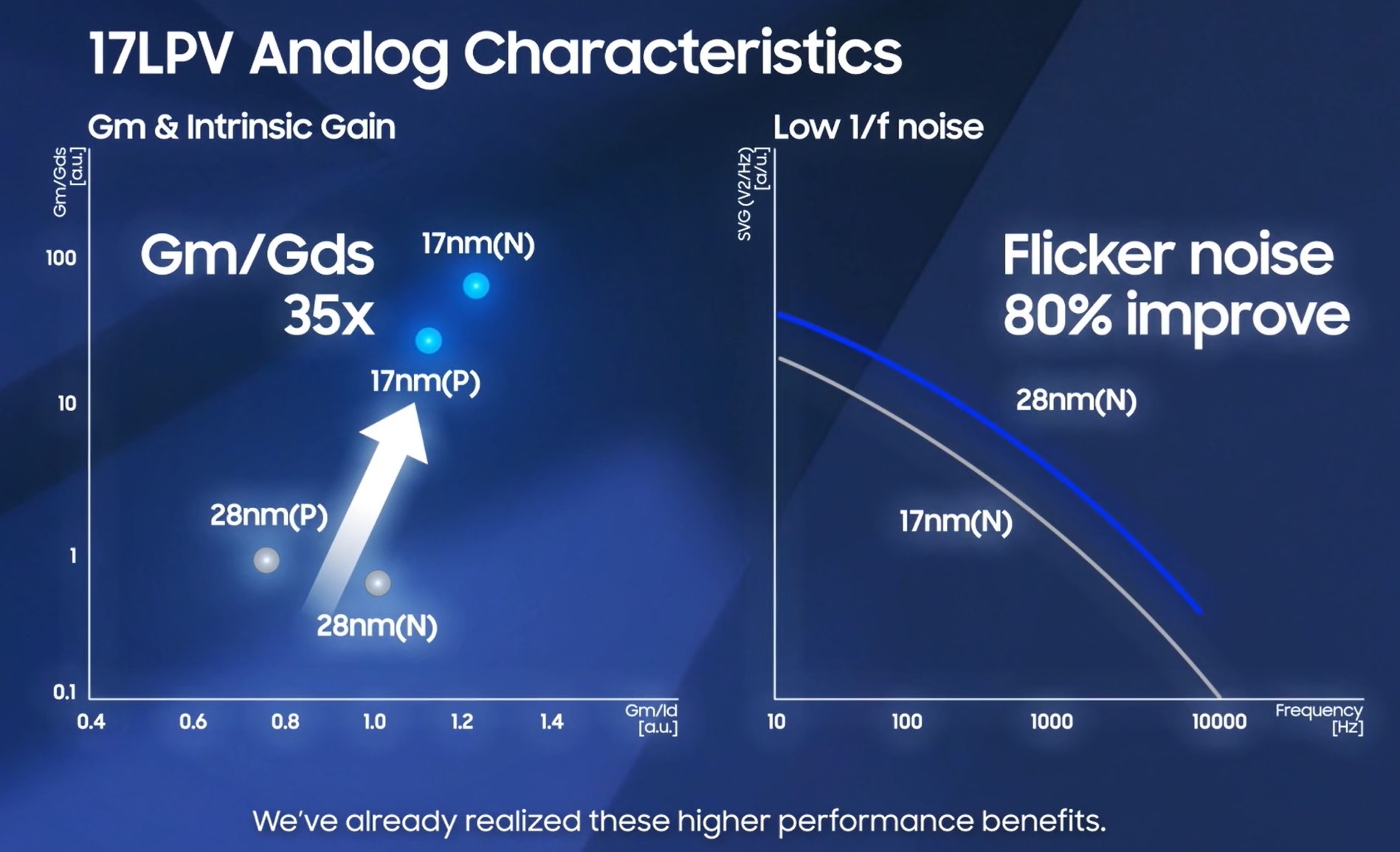

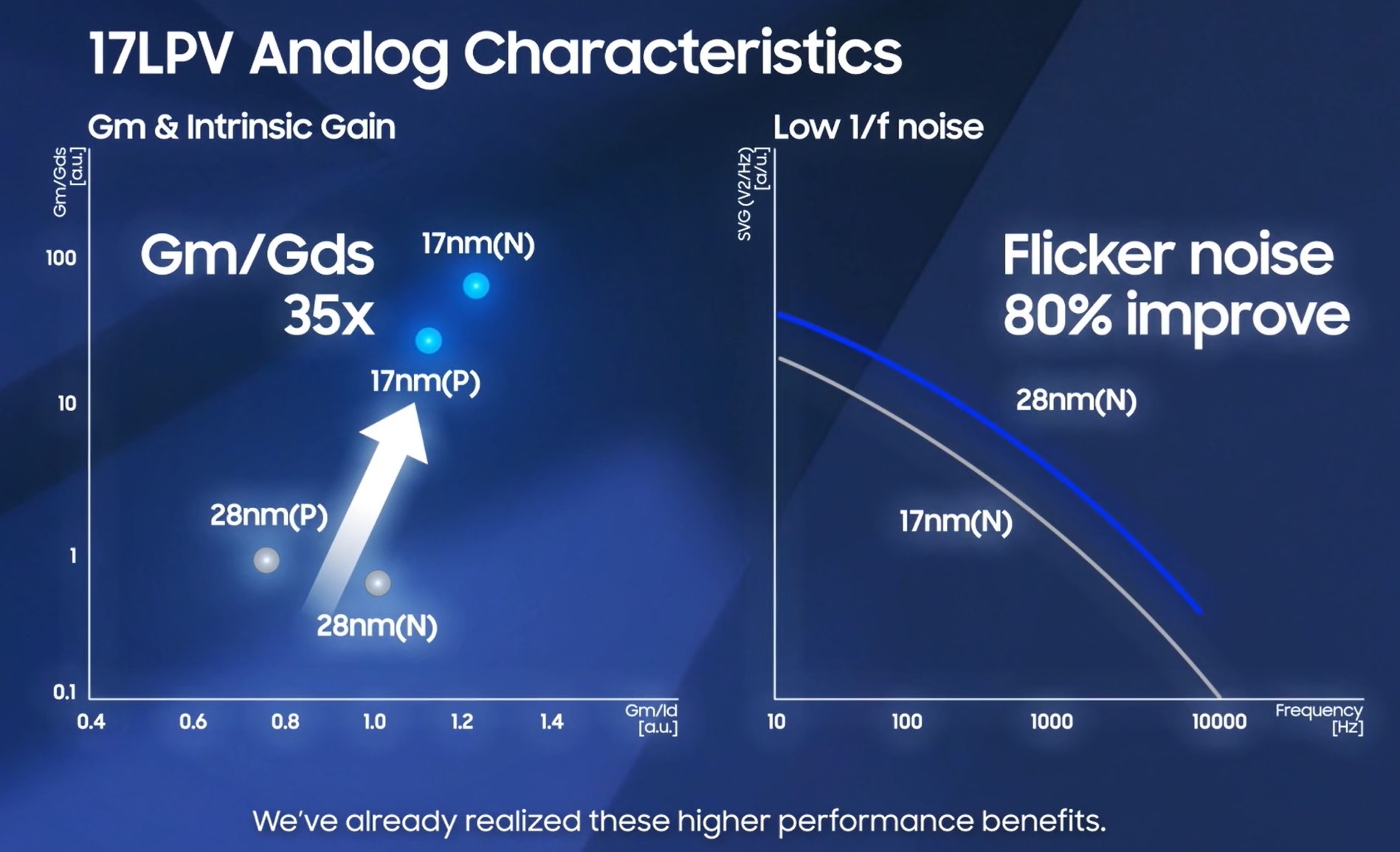

17LPV Analog Characteristics 그래프를 보면

28LPP랑 비교시 Gm/Gds Gain에서 무려 35배 오르고,

Flicker noise는 80% 향상 되었습니다.

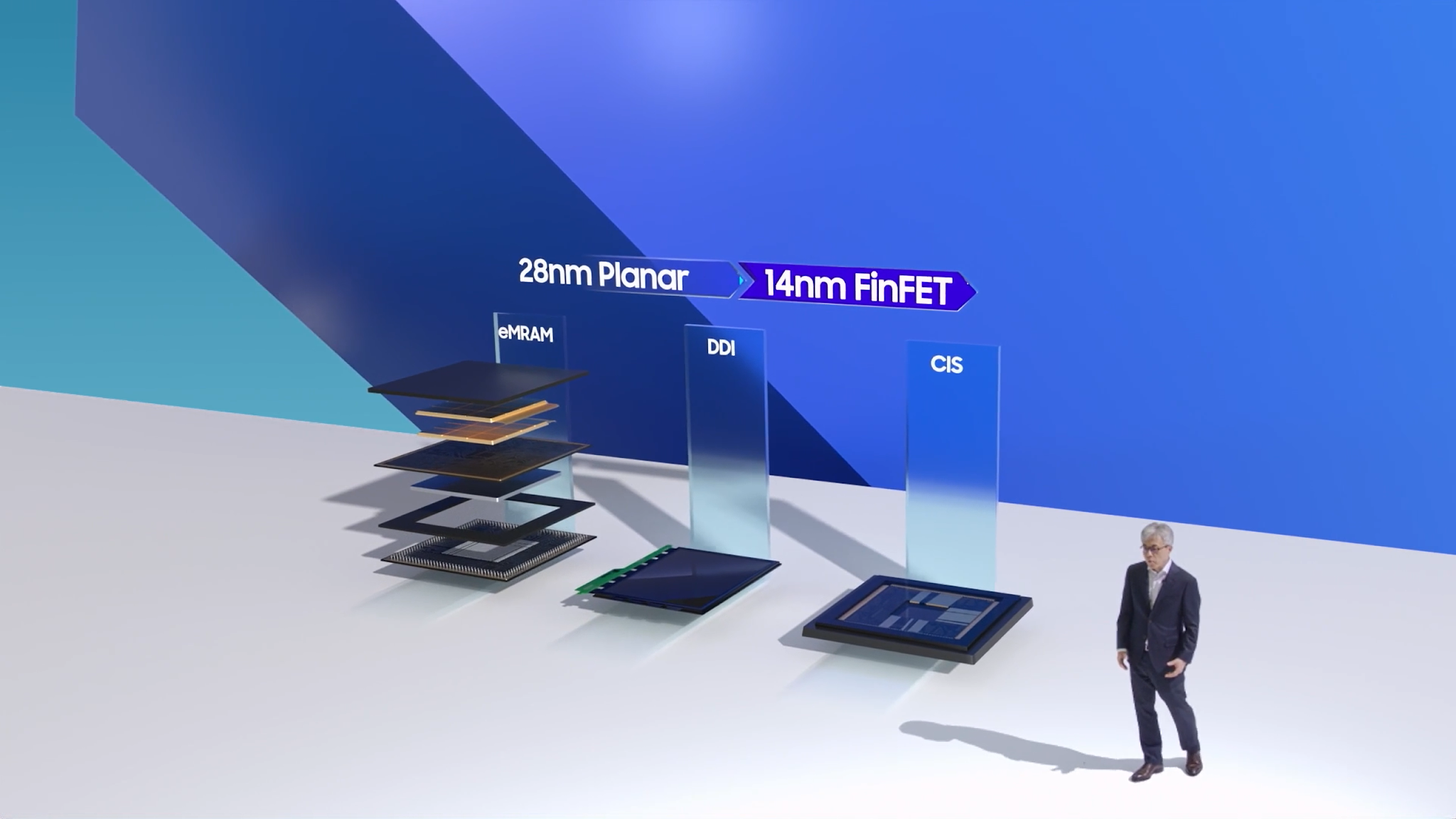

삼성파운드리는 17LPV 공정으로 eMRAM, DDI, CIS Logic를 제조할것이라 했으며

굉장히 극단적인 성능 향상으로 17LPV로 제조한 CIS Logic을 사용하면

600MP CIS에서 120DB의 넓은 DR에 8K@240fps 비디오 촬영이 가능하다라고 광고하고 있습니다.

8K에서 초당 240fps처리가 가능하면 50MP일 경우 시장통식으로 역산하면 초당 158fps 처리가

가능하다는 소리가 됩니다.

물론 온전히 50MP에서 158fps는 아닐겁니다.

왜냐면 CIS 특성상 비디오 모드일 경우, 초당 최대 속도 대비 프레임 보간을 통해 뻥튀기를 하니깐요.

그렇다면 그걸 감안하면 콩떼고 팥떼고 하면 17LPV CIS 로직에서 50MP일 경우 초당 60~90fps정도

보장을 할수있다는 소리가 됩니다.

초당 제로셔터렉이 보통은 해당 화소에서 24fps부터 광고하니 제로셔터렉 이상의 초당 처리가

확보되는겁니다.

물론 제조사는 이걸 제로셔터렉으로 이용하지 않고 셔터렉 여유만큼 후처리를 더 먹여서 화질을

높이는 방향으로 갈수도있어서 사용성 위주가 될것이냐 품질 위주가 될것이냐 선택은 여러가지가

될거같습니다.

최악이더라도 현재 12MP와 비슷한 수준으로 고화소 사용성이 증가한다는 소리가되니깐요.

여담으로

600MP라고하니 그게 생각나는군요.

예전에 언급되었던 4K/8K 비디오 촬영을 지원하는 600MP 0.8um 1/0.57" CIS가 있었죠.

저기서 언급되는 600MP가 해당 CIS일수도 있을거같습니다.

사이즈가 워낙 거대한놈이고 저건 사실상 17LPV로 CIS 하판 로직 만들면 저런 성능이

가능하다 정도로 보면될겁니다.

현존하는 8K 비디오 촬영을 지원하는 고화소 CIS들 로직이 28nm이고

그 한계는 8K@24~30fps가 한계입니다.

28LPP -> 17LPV 정도 변화의 CIS Logic이면

극단적인 비교로 28LPP 공정의 엑시노스5410/5420/5422와 14LPP의 엑시노스8890의 비교일겁니다.

17LPV의 성능이 14LPP보다 더 높으니 그 격차는 더 심하겠죠.

CPU, GPU처럼 어마어마한 고클럭을 요구하는게 아닌 ISP이다보니

설계에 더욱 용이하겠구요.

"그럼 미러리스나 DSRL용 풀프레임에 저런 FinFET 공정 적용해서 하판 로직 뽑으면 짱이겠네?"

물론 가능은 하지만 아무도 그런 시도는 하지않을겁니다.

못한다고 보는게 맞을듯하네요.

왜냐면 수지타산에 맞지않습니다.

당장 Sony A1 50MP 풀프레임 센서 스펙을 보면

상판은 90nm로 제조되고 (픽셀 사이즈가 워낙 거대해서 90nm 이상을 써야함)

하판은 TSMC 40nm로 제조되고 있습니다.

엄청 구공정이죠.

이런 구공정을 쓰는 이유는 단가 이슈도 크고 상판 수광부가 워낙 거대해서

이미 빛을 충분히 받고있는 상태에서 하판 로직 모바일 ISP마냥 그렇게 고성능일 필요가 없습니다.

(보장된 퀄리티)

당장 카메라 바디에 달리는 ISP칩 성능이 모바일 ISP와 10배 넘게 차이난다는것이 퀄콤 피셜이죠.

가뜩이나 90nm에 엄청 거대한 이미지 센서로 수율이나 단가 이슈가 있는데

최신 공정으로 로직까지 만들면 가격이 어마어마하게 비싸질겁니다.

그리고 저런 제품들 하판 로직의 경우

TSMC, 삼성 같은곳이 아니라 동부하이텍에서도 제조할텐데

죄다 최신공정쓰면 영세 파운드리 업체는 다 죽으라는 소리가 될 수있죠

정리하면 그렇습니다.

초고화소 CIS들은 상판 수광부 화질을 개선해도 하판 로직 성능이 떨어지면 한계가 명확하게 발생하고

이를 매꾸기 위해선 AP의 ISP+NPU를 통해 처리해야하는데 그러면 역시 속도 저하가 발생합니다.

이러한 문제를 해결하기 위해 나온것이 바로 하판 로직을 FinFET 공정으로 제조해서

CIS ISP 성능을 극대화 시켜서 속도, 품질, 소비전력을 개선하는겁니다.

극단적인 비교로 윗 언급처럼

28LPP 공정의 엑시노스5410/5420/5422와 14LPP의 엑시노스8890 이상의 차이 일수도 있겠구요.

이럴 경우 상대적으로 AP의 후처리에 대한 의존도 낮아져서 그동안 지적했던 고화소에서

사용성이 크게 오르게됩니다.

사용성이 아닌 품질 위주로 간다면 개선된 속도랑 소비전력 여유 만큼 후처리를 더욱 크게해서

화질을 높일수 있겠구요.....

현재 포착되는 차세대 CIS는 총 4가지 정도로

그중 3개는 삼성 시스템 반도체 물건으로 보입니다.

양산과 출시까지 아직 시간이 있어서 실제 나오고나서 판단해야겠지만

저는 굉장히 긍정적으로 봅니다.

일단 각종 지표들이 워낙 좋은 수치를 보여주고 있거든요.

발표 내용대로라면

28LPP 로직을 사용하는 100MP 와

17LPV 로직을 사용하는 600MP 비교시

- 소비전력 28% 개선

- 120DB HDR

- 8K@240fps 비디오 촬영

향상이됩니다.

2020년 ISCAS에서 발표한 65nm 상판과 14nm FinFET 하판 CIS 내용도 함께 적용하면

랜덤노이즈 20% 개선도 주 개선 내용에 포함할수도 있겠네요.

28LPP와 14LPP 성능 차이만 해도 어마어마한데 17LPV가 14LPP보다 성능이 높으니

단순히 계산해도 저 수치들이 허무맹랑한 수치는 아닐겁니다.

일단 해당 공정이 적용된 CIS들이 출시되는 타이밍이

시기상 3nm AP들도 상용화될 시기로 추정되기에 모바일 CIS들이 한번 큰 도약을하는

시기가 되지않을까 조심스레 추측해봅니다.

그런 의미에서 지금 28nm 로직의 고화소 CIS들은 정말 과도기일지도 모르겠습니다......

물론 이건 CIS 성능 관점에서 쓴 포스팅이고 제조사가 튜닝을 요상하게하면 그

건 또 다른 문제로 봐야할거같네요....ㅡㅡ;

이쪽 분야에선 사진은 구글, 비디오는 애플 이렇게 두명이 킹왕짱이라서요.

두 회사가 CIS 로직을 FinFET으로 바꿨을때 얼마나 큰 향상을 보여줄지 엄청 기대됩니다.

영양가 없는 긴글 읽어주셔서 감사합니다.

모바일 카메라 품질과 사용성 큰 도약을 위하여 ㅡㅡ/

cis 하나도 모르는데도 설명을 상세하게 써주셔서 재미있게 읽었습니다 ㅎㅎ